C’est un truc dont j’avais parlé il y a (très) longtemps : dans ses Fusion Drive, Apple n’a pas utilisé des SSD classiques, mais a optimisé le fonctionnement pour obtenir de bonnes performances, même avec un SSD d’une faible capacité.

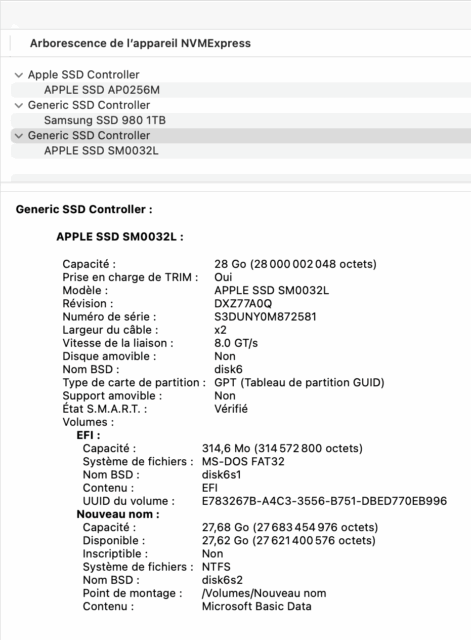

J’ai récupéré sur eBay un SM0032L, un SSD issu d’un iMac. C’est un modèle qui se retrouve habituellement dans un Fusion Drive, c’est-à-dire un bricolage d’Apple qui permettait d’unifier un SSD et un disque dur pour offrir un compromis entre performances et capacité. Le SSD sert uniquement de cache, avec un fonctionnement totalement transparent pour l’utilisateur, qui voit uniquement le HDD. C’est un compromis correct pour lancer les applications rapidement et éventuellement effectuer des transferts de petits fichiers, mais qui montre ses limites sur les tâches lourdes : les données se retrouvent rapidement sur le disque dur, avec les débits et la latence associés. Apple n’utilise plus de Fusion Drive depuis un moment, donc les composants se trouvent facilement.

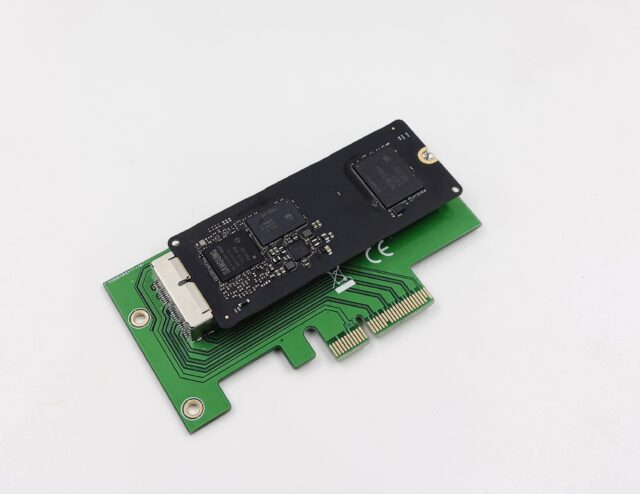

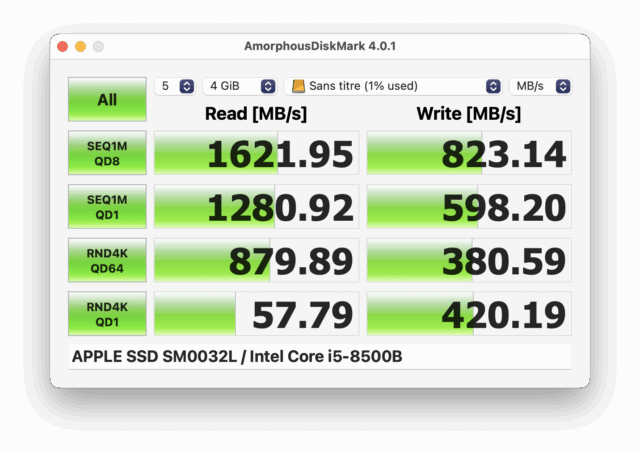

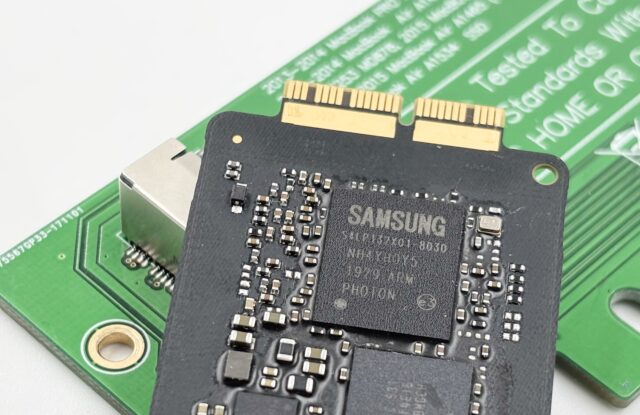

Le SSD est un modèle qui emploie le connecteur propriétaire d’Apple, proche du M.2. Il intègre un contrôleur NVMe et offre une capacité de 32 Go selon la référence, mais de 28 Go en pratique (il y a une partie de la capacité qui est réservée). Il est interfacé en PCI-Express 3.0 sur deux lignes, soit un débit maximal de l’ordre de 2 Go/s. Et dans la pratique, il atteint de très bons résultats : 1,6 Go/s en lecture (la limite réelle de ce genre d’interface) et 940 Mo/s en écriture (dans un PC). C’est une valeur très élevée pour un SSD de cette capacité : on tourne généralement à quelques centaines de Mo/s au mieux sur les modèles de petite capacité. Les performances sur les accès aléatoires sont aussi assez élevés.

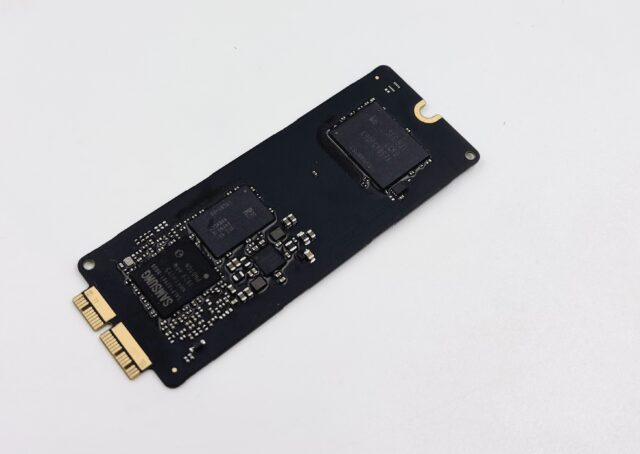

C’est évidemment ici qu’Apple triche : le SSD n’utilise pas de la mémoire MLC (deux bits) ou TLC (trois bits) mais directement une puce de mémoire SLC (un bit). Dans le modèle dont j’avais parlé en 2016, Apple employait une autre méthode : il y avait quatre puces de 16 Go de mémoire MLC (deux bits par cellule) configurée en mode pseudoSLC. Dans ce mode, la mémoire est simplement réglée pour n’employer qu’un seul bit par cellule au lieu de deux (ou trois), ce qui améliore les performances. Dans un SSD classique, c’est une solution employée comme cache : on configure une partie de l’espace dans ce mode pour écrire rapidement, avant de réécrire les données dans le mode natif pour garder l’avantage de la capacité.

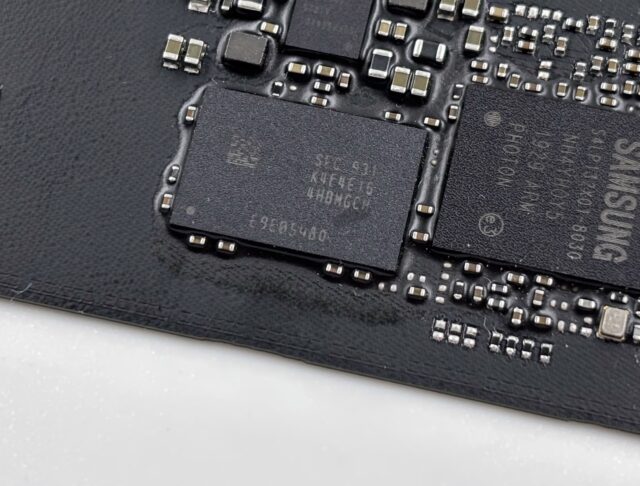

Mais la référence de l’unique puce de mémoire présente sur ce SSD (K9QFGY8S7A) indique bien qu’il s’agit directement d’une puce de mémoire SLC, sans passer par des artifices. Le contrôleur est un Samsung Photon, accompagné de (probablement) 512 Mo de mémoire LPDDR4 (je n’ai pas trouvé de décodeur pour la mémoire vive de ce type, référence K4F4E16-4HBMGCH).

Je pensais au départ qu’Apple passait par un mode pseudoSLC permanent dans tous les cas, mais ce n’est donc pas le cas ici. C’est peut-être plus économique de partir directement sur une puce de mémoire SLC de petite capacité que de mettre plusieurs puces de MLC ou de TLC configurée pour être employée en tant que SLC, je suppose.